# **RAIO**

# **RA8835**

# Dot Matrix LCD Controller Specification

Version 1.3 September 18, 2014

RAiO Technology Inc.

©Copyright RAiO Technology Inc. 2014

#### 1. Overview

The RA8835 is a controller IC that can display text and graphics on LCD panel. It can display layered text and graphics, scroll the display in any direction and partition the display into multiple screens. It also stores text, character codes and bitmapped graphics data in external frame buffer memory. Display controller functions include transferring data from the controlling microprocessor to the buffer memory, reading memory data, converting data to display pixels and generating timing signals for the buffer memory, LCD panel.

The RA8835 has an internal character generator with 160, 5 X 7 pixel characters in internal mask ROM. The character generators support up to 64, 8 X 16 pixel characters in external character generator RAM and up to 256, 8 X 16 pixel characters in external character generator ROM.

#### 2. Features

- Text, graphics and combined text/graphics display modes

- ◆ Three overlapping screens in graphics mode

- Up to 640 X 256 pixel LCD panel display resolution

- ♦ Programmable cursor control

- Smooth horizontal and vertical scrolling of all or part of the display

- ◆ 1/2-duty to 1/256-duty LCD drive

- Up to 640 X 256 pixel LCD panel display resolution memory

- ◆ 160, 5 X 7 pixel characters in internal mask-

- programmed character generator ROM

- Up to 64, 8 X 16 pixel characters in external character generator RAM

- Up to 256, 8 X 16 pixel characters in external character generator ROM

- ♦ 6800 and 8080 family microprocessor interfaces

- Low power consumption—3.5 mA operating current (V<sub>DD</sub> = 3.5V), 0.05 μA standby current

- Package:

RA8835P3N: QFP-60 pin (Lead Free) RA8835P4N: TQFP-60 pin (Lead Free)

◆ Power: 2.7 to 5.5 V

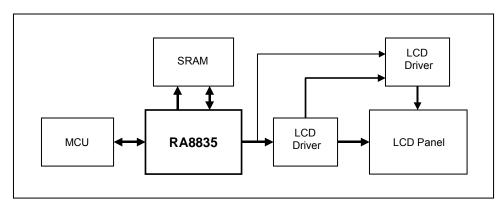

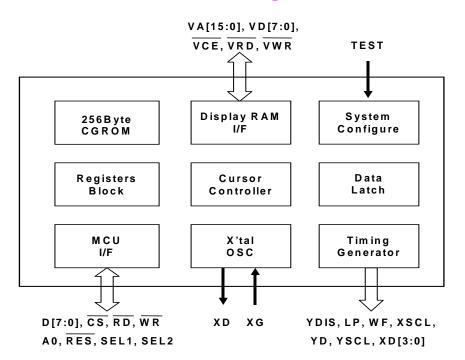

# 3. Block Diagram

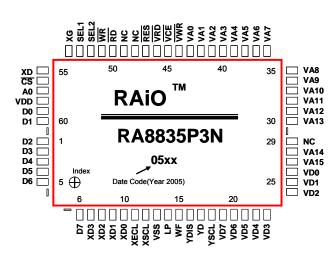

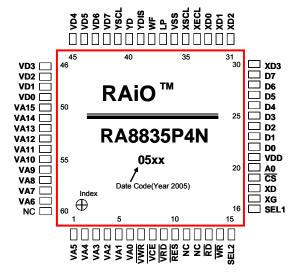

## 4. Package

Figure 4-1: RA8835P3N(QFP-60 Pin)

Figure 4-2: RA8835P4N (TQFP-60 Pin)

# 5. Pin Descriptions

#### 5.1.1. MCU Interface

| Pin Name      | Function                                                                                                                                                                   |                                      |                                    |             |           |            |              |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------|-------------|-----------|------------|--------------|--|

| D0 to D7      | MCU Data Bus.  Tri-state input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus.                                                                      |                                      |                                    |             |           |            |              |  |

|               | MCU Interface Select.  The RA8835 series supports both 8080 family processors (such as the 8085 and Z80®) and 6800 family processors (such as the 6802 and 6809).          |                                      |                                    |             |           |            |              |  |

|               | SEL1                                                                                                                                                                       | SEL2*                                | Interface                          | A0          | RD        | WR         | CS           |  |

| SEL1,<br>SEL2 | 0                                                                                                                                                                          | 0                                    | 8080<br>family                     | A0          | RD        | WR         | cs           |  |

|               | 1                                                                                                                                                                          | 0                                    | 6800<br>family                     | A0          | Е         | R/W        | cs           |  |

|               | SEL1 should be tied directly to VDD or VSS to prevent noise. If noise does appear on SEL1, decouple it to ground using a capacitor placed as close to the pin as possible. |                                      |                                    |             |           |            |              |  |

| RD<br>or<br>E | read strobe.<br>active.                                                                                                                                                    | 080 family<br>The RA88<br>800 family | ole. interface is s 335 series out | put buffers | are enabl | ed when th | is signal is |  |

| Pin Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                 |   |                  |                 |                                      |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|-----------------|--------------------------------------|--|

| WR<br>or<br>R/W | Write Control or Read/Write Control.  When the 8080 family interface is selected, this signal acts as the active-LOW write strobe. The bus data is latched on the rising edge of this signal.  When the 6800 family interface is selected, this signal acts as the read/write control signal. Data is read from the RA8835 series if this signal is HIGH, and written to the RA8835 series if it is LOW. |   |                  |                 |                                      |  |

| CS              | Chip Select. This active-LOW input enables the RA8835 series. It is usually connected to the output of an address decoder device that maps the RA8835 series into the memory space of the controlling microprocessor.                                                                                                                                                                                    |   |                  |                 |                                      |  |

|                 | Command/Data Select. 8080 Family Interface:                                                                                                                                                                                                                                                                                                                                                              |   |                  |                 |                                      |  |

|                 | A                                                                                                                                                                                                                                                                                                                                                                                                        | 0 | RD               | $\overline{WR}$ | Function                             |  |

|                 | (                                                                                                                                                                                                                                                                                                                                                                                                        | ) | 0                | 1               | Status flag read                     |  |

|                 | ,                                                                                                                                                                                                                                                                                                                                                                                                        | l | 0                | 1               | Display data and cursor address read |  |

|                 | (                                                                                                                                                                                                                                                                                                                                                                                                        |   | 1                | 0               | Display data and parameter write     |  |

| 4.0             |                                                                                                                                                                                                                                                                                                                                                                                                          |   | 1                | 0               | Command write                        |  |

| A0              | 6800 Family Interface:                                                                                                                                                                                                                                                                                                                                                                                   |   |                  |                 |                                      |  |

|                 | A                                                                                                                                                                                                                                                                                                                                                                                                        | 0 | $R/\overline{W}$ | Е               | Function                             |  |

|                 | (                                                                                                                                                                                                                                                                                                                                                                                                        | ) | 1                | 1               | Status flag read                     |  |

|                 | ,                                                                                                                                                                                                                                                                                                                                                                                                        |   | 1                | 1               | Display data and cursor address read |  |

|                 | (                                                                                                                                                                                                                                                                                                                                                                                                        | ) | 0                | 1               | Display data and parameter write     |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                          |   | 0                | 1               | Command write                        |  |

| RES             | Hardware Reset.  This active-LOW input performs a hardware reset on the RA8835 series. It is a Schmitt-trigger input for enhanced noise immunity; however, care should be taken to ensure that it is not triggered if the supply voltage is lowered.                                                                                                                                                     |   |                  |                 |                                      |  |

## **5.1.2 Display Memory Control**

The RA8835 series can directly access static RAM and PROM. The designer may use a mixture of these two types of memory to achieve an optimum trade-off between low cost and low power consumption.

| Pin Name    | Function                                                                                                                                             |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VA0 to VA15 | <b>16-bit Display Memory Address.</b> When accessing character generator RAM or ROM, VA0 to VA3, reflect the lower 4 bits of the RA8835 row counter. |  |  |

| VD0 to VD7  | Display Memory Data Bus.  8-bit tri-state display memory data bus. These pins are enabled when VRD or VWR is LOW.                                    |  |  |

| VWR         | Display Memory Write Control.  Active-LOW display memory write control output.                                                                       |  |  |

| VRD         | Display Memory Read Control.  Active-LOW display memory read control output.                                                                         |  |  |

| Pin Name | Function                                                                  |  |  |

|----------|---------------------------------------------------------------------------|--|--|

| VCE      | Display Memory Chip Select.                                               |  |  |

|          | Active-LOW static memory standby control signal. VCE can be used with CS. |  |  |

## 5.1.3 LCD Drive Signals

In order to provide effective low-power drive for LCD matrixes, the RA8835 series can directly control both the X- and Y-drivers using an enable chain.

| Pin Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XD0 to XD3 | Data Output for Driver. 4-bit X-driver (column drive) data outputs. Connect these outputs to the inputs of the X-driver chips.                                                                                                                                                                                                                                                                                                                      |

| XSCL       | Latch Clock.  The falling edge of XSCL latches the data on XD0 to XD3 into the input shift registers of the X-drivers. To conserve power, this clock halts between LP and the start of the following display line (See section 6.3.7).                                                                                                                                                                                                              |

| XECL       | <b>Trigger Clock for Chain Cascade.</b> The falling edge of XECL triggers the enable chain cascade for the X-drivers. Every 16th clock pulse is output to the next X-driver.                                                                                                                                                                                                                                                                        |

| LP         | Latch Pulse.  LP latches the signal in the X-driver shift registers into the output data latches.  LP is a falling-edge triggered signal, and pulses once every display line.  Connect LP to the Y-driver shift clock on modules.                                                                                                                                                                                                                   |

| WF         | AC Drive Output.  The WF period is selected to be one of two values with SYSTEM SET command.                                                                                                                                                                                                                                                                                                                                                        |

| YSCL       | Latch Clock for YD.  The falling edge of YSCL latches the data on YD into the input shift registers of the Y-drivers. YSCL is not used with driver ICs which use LP as the Y-driver shift clock.                                                                                                                                                                                                                                                    |

| YD         | Data Pulse Output for Y Drivers.  It is active during the last line of each frame, and is shifted through the Y drivers one by one (by YSCL), to scan the display's common connections.                                                                                                                                                                                                                                                             |

| YDIS       | Power-down Output Signal. YDIS is HIGH while the display drive outputs are active. YDIS goes LOW one or two frames after the sleep command is written to the RA8835 series. All Y-driver outputs are forced to an intermediate level (de-selecting the display segments) to blank the display. In order to implement power-down operation in the LCD unit, the LCD power drive supplies must also be disabled when the display is disabled by YDIS. |

#### 5.1.4. Oscillator and Power

| Pin Name | Function                                                                                                                                                                          |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| XG       | Crystal Connection for Internal Oscillator  This pin can be driven by an external clock source that satisfies the timing specifications of the EXT f0 signal (See section 7.3.6). |  |  |

| XD       | Crystal Connection for Internal Oscillator Leave this pin open when using an external clock source.                                                                               |  |  |

| VDD      | 2.7 to 5.5V Supply.  This may be the same supply as the controlling microprocessor.                                                                                               |  |  |

| GND      | Ground                                                                                                                                                                            |  |  |

| TEST     | Test Pin. This is a test pins. No need for connection(NC).                                                                                                                        |  |  |

**Note:** The peak supply current drawn by the RA8835 series may be up to ten times the average supply current. The power supply impedance must be kept as low as possible by ensuring that supply lines are sufficiently wide and by placing 0.47µF decoupling capacitors that have good high-frequency response near the device's supply pins.

# 6. System Application